Rain科技11月30日消息,作为当前半导体晶圆代工领域的领军者,台积电的发展动向备受市场瞩目。随着工艺技术不断逼近1nm节点,其未来的发展潜力究竟如何?本文将为您解析台积电最新公布的工艺路线图。

在近期举办的开放创新平台生态系统论坛上,台积电详细展示了未来几年的逻辑工艺发展蓝图。以2025年为中心,当前已实现量产的FinFET技术将涵盖3nm系列,具体包括N3、N3E、N3P、N3X以及N3C等多种改进版本。

技术发展的新篇章将在2nm节点开启,届时将引入Nanosheet晶体管架构,这一技术即GAA(Gate-All-Around)或称环绕栅极晶体管的实际应用。值得关注的是,率先采用这一先进工艺的将是AMD的Zen6架构EPYC处理器,预计于明年下半年量产上市。

在2nm节点之后,台积电还将推出N2P和N2X工艺。值得注意的是,在N2和N2P/N2X之间,将引入一项名为A16 SPR的特殊工艺。A16 SPR中的SPR代表了台积电创新的背面供电技术Super Power Rail。相较于Intel的PowerVia技术,台积电的SPR在设计理念和技术实现上可能存在显著差异,其具体优势和效果,还需待产品实际量产后进行严谨的验证和对比。

实际上,A16 SPR工艺是台积电在早期2nm节点规划基础上进行调整的产物。通过将GAA技术与背面供电技术的分步量产,台积电展现了其灵活的策略,避免了三星和Intel在同一代工艺上同时引入这两项革命性技术所可能带来的风险。

再往后,A14节点将是又一个具有里程碑意义的重大技术更新。该节点将GAA技术与背面供电技术进行整合,有望在性能和能效方面带来更为显著的提升,为下一代高端芯片的开发奠定坚实基础。

台积电此次公布详细的工艺路线图,旨在增强客户对其未来技术迭代能力的信心,确保在未来数年内维持每年推出新工艺的节奏,并且每代工艺都能在性能和能效方面实现稳步且可预期的提升。

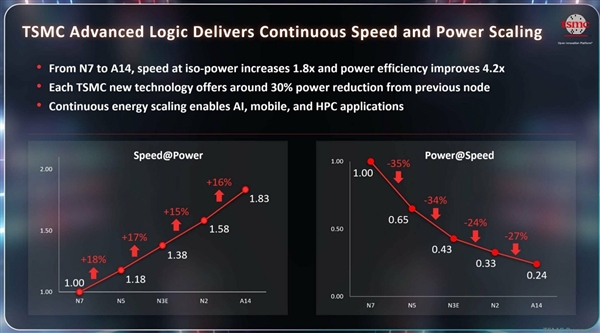

以2018年的7nm节点N7为基准,台积电数据显示,在同等功耗下,后续每一代工艺的性能提升幅度都保持在15%至18%之间。同时,在实现相同性能的前提下,功耗也得到了显著降低。从N7到N3,每一代工艺的功耗降低了1/3以上。尽管从N3到未来的A14节点,功耗的降低幅度可能略微放缓至每代25%左右,但整体的能效优化趋势依然显著。

台积电特别提到,与N7相比,A14工艺在同等功耗下能够实现83%的性能提升,能效更是达到了3.2倍的飞跃。这意味着,从2018年到2028年这十年间,芯片工艺的性能提升约80%。

对于这一数据,若与经典的“摩尔定律”相比,可能会让人感到些许“失望”。然而,业界普遍认可,在28nm节点之后,传统意义上的摩尔定律已经逐渐失效。在当前技术条件下,实现80%的性能提升已属不易,充分体现了半导体制造工艺的持续进步和技术瓶颈的挑战。

作为参考,2018年的N7工艺代表芯片如苹果A12,其最高频率约为2.5GHz,晶体管数量为69亿。而到了如今,A18 Pro处理器已能达到4GHz的频率,晶体管数量达到200亿。展望未来,在A14节点到来之际,处理器频率达到5GHz、晶体管规模突破300亿,是完全可以期待的。