Rain科技1月10日报道,台积电在去年底已按计划宣布其2纳米(2nm)工艺实现量产,这一工艺技术预计将成为今年的重头戏。首批搭载该先进工艺的将是AMD的EPYC Venice(霄龙热那瓦)处理器。

紧随其后,苹果iPhone 18系列将搭载的A20芯片、高通骁龙8E6 Pro以及联发科天玑9600等下一代旗舰芯片,也将采用台积电的2nm工艺。为满足日益增长的市场需求,台积电计划在一年内将其2nm产能从每月3.5万片晶圆大幅提升至14万片,以期将其打造成公司营收的重要支柱之一。

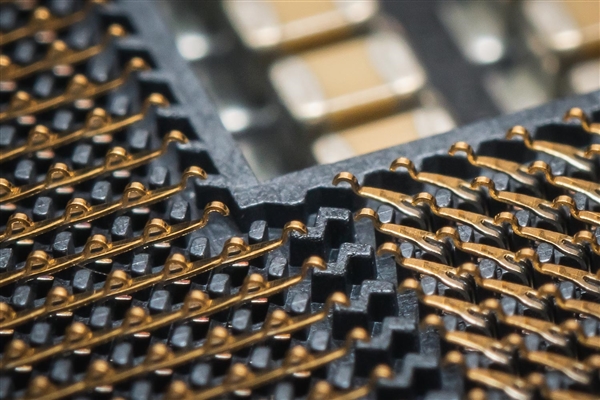

2nm工艺的引入,在台积电的工艺研发历程中具有里程碑式的意义。这是公司历史上第二次对其核心的晶体管架构进行颠覆性升级,正式转向了GAA(Gate-All-Around,全环绕栅极)晶体管架构。这一技术革新预示着半导体制造正在进入一个全新阶段。

回顾台积电的工艺演进史,上一次重大的晶体管架构变革发生在2014年,标志性的16纳米(16nm)工艺首次实现了从平面晶体管向FinFET(鳍式场效应晶体管)这一3D晶体管结构的飞跃。FinFET的引入,极大地提升了晶体管的性能和能效,为移动计算的蓬勃发展奠定了基础。

提及晶体管技术的演变,令人不禁联想到十几年前的半导体行业的格局。彼时,英特尔曾自信地宣称其工艺技术领先友商三年半,这一说法并非空穴来风。早在2011年,英特尔便已实现22纳米3D晶体管工艺的量产,并在其2012年的IVB(Ivy Bridge)处理器上正式应用。与此同时,台积电和三星等同行当时仍以28纳米工艺为主流,技术差距远大于当前台积电在先进工艺上对英特尔的相对优势。

如今,半导体行业的竞争格局已悄然改变。台积电在先进工艺节点上展现出“稳健推进、快速量产”的特点,并在2nm工艺上仅进行了GAA晶体管架构的升级。面向未来,台积电规划中的1.6纳米(1.6nm)A16工艺将进一步引入背面供电(Backside Power Delivery)技术。此举旨在进一步克服物理极限,提升芯片的集成密度和性能表现,尤其对高性能计算(HPC)类产品而言,将带来显著的性能飞跃。

在A16工艺之后,台积电还将继续推进1.4纳米(1.4nm)级别的A14工艺。该工艺将继续深化对GAA架构的改进,并结合背面供电技术,以期在性能和效率上取得更佳的平衡。

而更长远的未来,1纳米(1nm)节点的突破将是行业的终极目标之一。目前,尚无任何厂商能够明确宣布1nm及以下工艺的量产时间表,这些技术仍处于积极的研发阶段。届时,晶体管结构可能再次迎来颠覆性升级,例如向CFET(Complementary Field-Effect Transistor,互补场效应晶体管)演进,以实现更高的集成度和更小的尺寸。

与此同时,半导体材料也在持续不断地进化。台积电已经开始探索2D材料甚至1D材料的应用潜力。这些新型材料的引入,有望为克服晶体管尺寸缩小所带来的物理挑战提供新的解决方案,打开半导体技术发展的新思路。

需要指出的是,台积电目前提及的诸如2D、1D材料等前瞻性技术,仍处于概念探索阶段,尚未进入实质性的研发落地。因此,未来1nm及以下工艺的量产时间、最终性能表现以及具体技术路径,都存在极大的不确定性,过早地对其进行预测尚为时过早。